填補網絡安全勞動力缺口 網絡與信息安全軟件開發的挑戰與機遇——基于CSIS報告的視角

隨著全球數字化轉型的加速和網絡威脅的日益復雜化,網絡安全已成為國家安全、經濟穩定和社會運行的核心基石。美國戰略與國際問題研究中心(CSIS)等多份權威報告持續警示,全球正面臨嚴峻的網絡安全專業人才短缺問題,其中,專注于網絡與信息安全軟件開發的高端、復合型人才缺口尤為突出。這一缺口不僅制約了創新安全工具與防護體系的構建,更直接影響了國家與企業在數字空間的防御能力和韌性。

一、 缺口現狀:需求激增與供給不足的結構性矛盾

CSIS報告指出,網絡安全勞動力缺口是系統性和全球性的。具體到網絡與信息安全軟件開發領域,這一矛盾體現得更加尖銳:

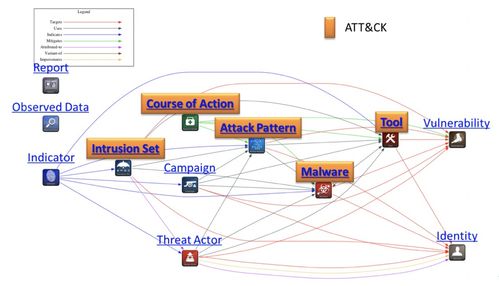

- 需求側爆炸式增長:云計算、物聯網、人工智能、5G等新技術的普及,極大擴展了網絡攻擊面。傳統的邊界防護已不足夠,需要深度集成安全能力的軟件(即“安全左移”和原生安全),這催生了對能夠開發安全編碼、漏洞管理、威脅檢測、隱私增強技術等核心工具和平臺的開發者的巨大需求。

- 供給側能力脫節:市場上大量通用軟件開發人員缺乏系統的網絡安全知識(如安全開發生命周期、常見漏洞與暴露、加密技術等),而傳統的網絡安全專家往往又缺乏扎實的軟件開發與架構設計能力。能夠橫跨兩個領域,既懂攻防又精于編碼的“安全開發工程師”或“安全軟件架構師”極為稀缺。

二、 深層原因:跨越技術與認知的鴻溝

造成這一專項缺口的原因是多層次的:

- 技能復合性要求高:優秀的網絡信息安全軟件開發人員需要融合多項技能:精通編程語言與軟件工程、深刻理解網絡協議與系統漏洞、熟悉安全合規框架、并具備一定的攻擊者思維。這種“T型”或“π型”知識結構培養周期長、難度大。

- 教育與培訓體系滯后:許多高校的計算機科學課程中,網絡安全尚未成為與數據結構、算法同等重要的核心模塊。專門的網絡安全專業則可能偏重理論、管理與防御策略,在深度開發實踐上投入不足。企業內部的在職培訓也往往難以跟上技術迭代的速度。

- 行業認知與資源錯配:部分組織仍將安全視為IT的附加功能,而非軟件開發的內在組成部分,導致對安全開發崗位的投入和重視程度不夠,薪酬競爭力與職業發展路徑不如純商業軟件開發崗位清晰,難以吸引頂尖人才。

三、 核心影響:從創新乏力到系統性風險

網絡安全軟件開發人才的短缺,帶來了一系列連鎖反應:

- 安全產品創新受阻:缺乏足夠的一流開發者,導致主動防御、智能威脅狩獵、自動化響應等先進安全工具的研發和迭代速度放緩。

- 軟件供應鏈風險加劇:企業被迫更多地依賴第三方或開源安全組件,而這些組件本身也可能存在未知漏洞,增加了供應鏈被攻擊的風險。

- 企業安全基礎薄弱:無法自研或深度定制安全軟件,使得許多企業(尤其是關鍵基礎設施運營者)的防御體系停留在被動修補的階段,難以應對高級持續性威脅。

四、 填補缺口:多元路徑與協同策略

基于CSIS報告的建議與行業最佳實踐,解決這一缺口需要政府、教育界、企業和行業組織多方協同:

- 教育改革與課程融合:推動高校在計算機科學、軟件工程專業中強制性嵌入安全編碼、軟件安全等核心課程;同時發展網絡安全與軟件工程的雙學位或微專業項目。推廣“以賽代練”,通過CTF奪旗賽、安全開發馬拉松等激發學生興趣。

- 企業主導的實踐培養:企業應建立更完善的內部“安全開發”培訓體系,設立明確的學徒制或輪崗計劃,讓開發人員深入安全團隊,也讓安全人員參與開發項目。加大對內部安全工具平臺開發的資源投入。

- 政策激勵與標準引導:政府可通過稅收優惠、研發補助等方式,鼓勵企業投資于安全軟件開發人才培養和工具自研。推動建立網絡信息安全軟件開發人員的技能認證標準,提升職業認可度。

- 開源社區與生態共建:鼓勵和支持開源安全軟件項目,這既是重要的公共產品,也是培養和識別人才的絕佳平臺。通過社區協作,降低創新門檻,加速知識傳播。

結論

CSIS報告所揭示的網絡安全勞動力缺口,尤其在網絡與信息安全軟件開發這一關鍵維度上,是一個關乎數字時代根本安全的戰略議題。填補這一缺口,不能僅靠市場自發調節,而需要一場系統性的“人才革命”。它要求我們重新定義軟件開發者的技能圖譜,重塑人才培養模式,并提升安全開發在整個技術價值鏈中的地位。唯有建立起一支既能夠構筑數字世界、又能夠堅實守護它的開發力量,我們才能在日益激烈的網絡空間競爭中贏得主動,筑牢數字發展的安全底座。

如若轉載,請注明出處:http://www.kwny.com.cn/product/52.html

更新時間:2026-03-18 20:29:34